Superconducting Qubit Quantum Computer (SQQC)

To operate a quantum processor in the noisy intermediate-scale quantum (NISQ) era the Superconducting Qubit Quantum Computer (SQQC) consortium will implement fast (re-)calibration and tune-up schemes including specific firmware for the operation of generalized types of qubits. Efficient optimization algorithms including real-time pulse sequencing and high-fidelity reset operations for high trigger rates will be developed. In collaboration with the THEQUCO, Q-DESSI and HAT consortia, the SQQC consortium will then develop and run benchmark algorithms in a high-performance computing environment at elevated operation speed.

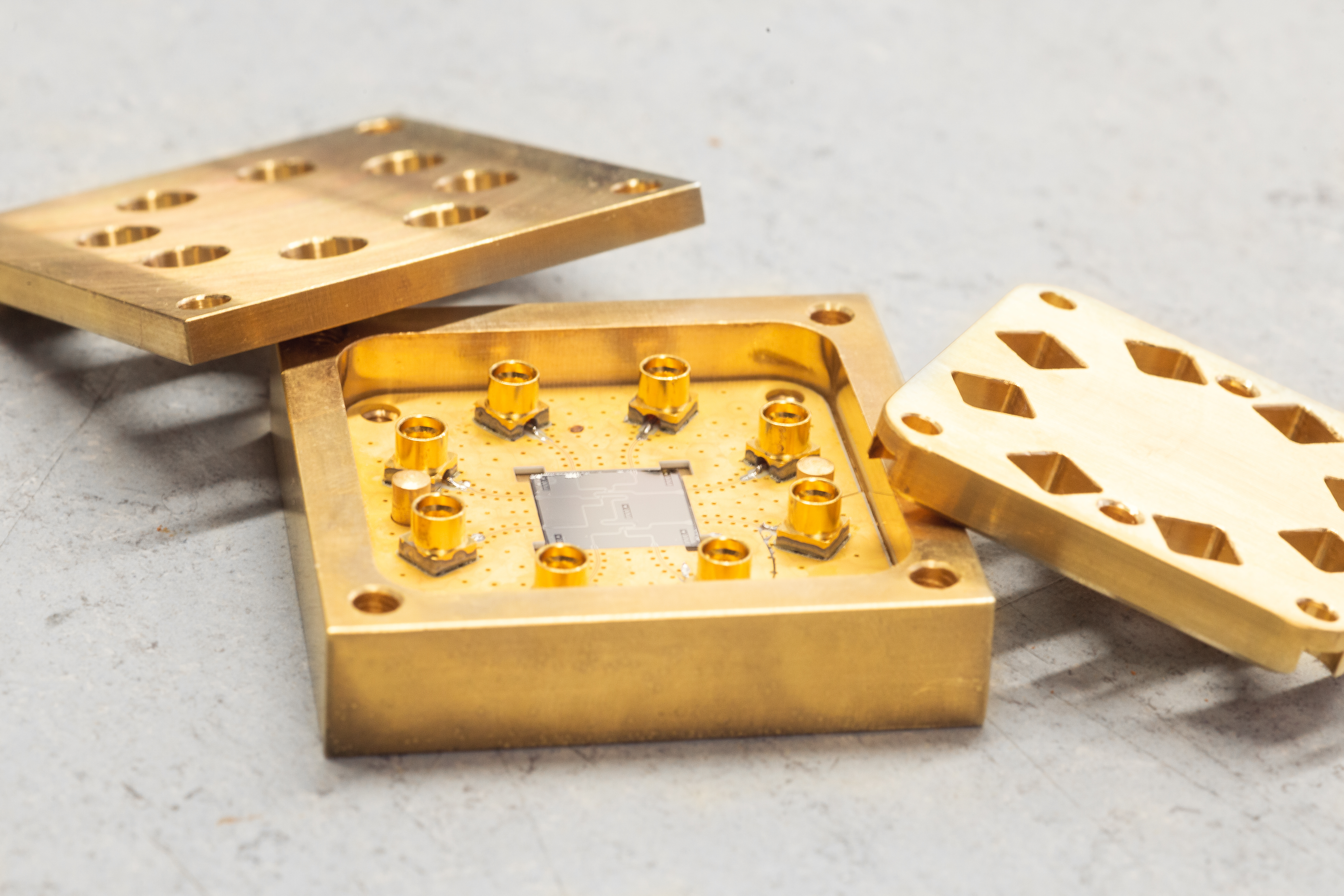

A further key goal of this consortium is the improvement of the coherence time of superconducting quantum circuits as a prerequisite for the successful operation of quantum algorithms on scalable architectures. Novel materials, enhanced fabrication processes and alternative types of superconducting qubits with small footprint are being investigated. To reach the project goals, the SQQC consortium will closely collaborate with the SHARE consortium and KQTPE on scalable fabrication, hetero-integration and packaging technology.

To realize two-qubit gate fidelities exceeding 99% both in planar chip geometries and in scalable 3D integrated quantum processors, the materials and fabrication effort will be supported by the development of optimal control methods and characterization schemes together with the HAT consortium and by full-processor benchmarking tools with the THEQUCO consortium. By developing non-reciprocal on-chip microwave components the SQQC consortium aims to enhance the system scalability, improve qubit readout and develop fast feedback control electronics for direct integration into a high-performance computing environment in collaboration with the Q-DESSI and SHARE consortia.